Welcome to the world of RISC V Architecture, where simplicity meets adaptability. In this tutorial, we will unravel the complexities of this revolutionary instruction set architecture, empowering you to dive into the realm of efficient and customizable computing.

V Cores

One of the advantages of V Cores is their simplicity. They use a reduced instruction set computer (RISC) architecture, which means they have a smaller set of instructions compared to complex instruction set computers (CISC). This simplicity allows for faster execution and easier debugging.

V Cores can also be multi-core processors, meaning they have multiple cores on a single chip. This enables parallel processing, where multiple tasks can be executed simultaneously, resulting in faster overall performance.

In terms of microarchitecture, V Cores often use superscalar processors, which can execute multiple instructions per clock cycle. They also have CPU caches, which are small, high-speed memory units that store frequently accessed data. This helps improve performance by reducing the time it takes to access data from the main memory.

V Cores can be simulated using emulators like Verilator, which allows for testing and debugging before the actual hardware is available. They can also handle interrupts, which are signals that pause the execution of a program to handle a specific event, such as a timer or input/output request.

V Cores are commonly used in various applications, ranging from mainframe computers to embedded systems. They are versatile and can be found in a wide range of devices, from smartphones to AI accelerators.

Some notable companies and organizations involved in the development and adoption of V Cores include SiFive, IBM, and Google. The RISC-V architecture itself was developed at the University of California, Berkeley.

V System

One of the key advantages of the V System is its support for multi-core processors, allowing for parallel processing and increased performance. This makes it ideal for tasks that require high computational power, such as artificial intelligence and data analysis.

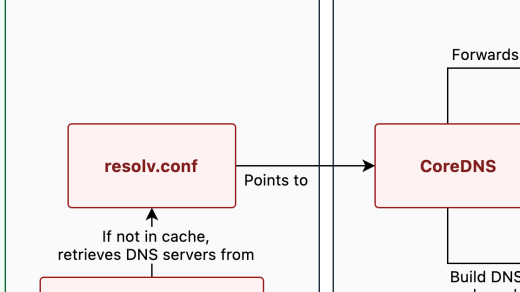

For those interested in learning more about the V System and RISC-V architecture, there are various resources available. Emulators and simulators can be used to run and test code, providing a hands-on learning experience. Verilator is a popular emulator that can be used to simulate and analyze the behavior of a V System design.

Additionally, there are several open-source projects and communities dedicated to the development and improvement of the V System. GitHub hosts many repositories related to the V System, where users can find code examples, tutorials, and collaborate with others.

To get started with the V System and RISC-V architecture, it is recommended to have a basic understanding of computer architecture and programming. Knowledge of concepts such as machine code, computer memory, and software will be beneficial.

Taking Linux training can also be beneficial, as the V System is often used in conjunction with the Linux operating system. Linux is a powerful and versatile operating system that is widely used in the industry, making it a valuable skill to have.

V

One of the key advantages of RISC-V is its modular and extensible nature, allowing for easy customization and adaptation to different applications. It supports superscalar processors, multi-core processors, and out-of-order execution, making it suitable for a wide range of computing tasks.

RISC-V also provides a high level of flexibility when it comes to microarchitecture and CPU cache design. It allows developers to optimize performance by fine-tuning the memory hierarchy and implementing efficient caching strategies.

For those interested in learning more about RISC-V, there are several resources available. The RISC-V Foundation offers an emulator and a simulator that enable you to experiment with RISC-V programs and understand its execution process. Additionally, there are open-source implementations of the RISC-V architecture, such as SiFive’s Core IP, which provide a hands-on experience in building RISC-V-based systems.

If you are considering taking Linux training, understanding RISC-V architecture can be beneficial. Linux, being an open-source operating system, has been ported to the RISC-V architecture, providing an opportunity to explore the synergy between open-source software and open-source hardware.

To dive deeper into RISC-V, you can explore the RISC-V ecosystem on platforms like GitHub, where you can find various projects, libraries, and tools related to the architecture. You can also find tutorials and educational materials from reputable institutions like the University of California, Berkeley.

By familiarizing yourself with RISC-V, you can gain valuable knowledge and understanding of computer architecture, which is essential for both software and hardware development. Whether you are interested in system-on-a-chip design, artificial intelligence accelerators, or embedded systems, RISC-V offers a versatile platform to expand your skills and expertise.

V Architecture

| Feature | Description |

|---|---|

| Open Standard | RISC-V (pronounced as “risk-five”) is an open-source instruction set architecture (ISA) that allows anyone to design, manufacture, and sell RISC-V chips and software. |

| Simplicity | RISC-V follows a Reduced Instruction Set Computer (RISC) approach, which keeps the instruction set small and simple, making it easier to understand and implement. |

| Modularity | The RISC-V architecture is designed with a modular structure, allowing users to choose and implement only the necessary components, reducing complexity and enhancing customization. |

| Scalability | RISC-V supports a wide range of applications, from small microcontrollers to large-scale server systems, making it highly scalable and adaptable. |

| Extensibility | With its extensible design, RISC-V allows users to add custom instructions and features, enabling efficient implementation of domain-specific optimizations. |

| Portability | RISC-V is platform-independent, allowing software written for one RISC-V system to run on any other RISC-V system, promoting software portability and compatibility. |