Unleashing the Power of RISC-V: A Comprehensive Assembly Tutorial

Introduction to RISC-V Assembly Programming

In this RISC-V Assembly Tutorial, we will provide a comprehensive introduction to RISC-V assembly programming. We will cover the basics of assembly language and how it relates to the RISC-V instruction set architecture. Whether you are a beginner or have experience with other assembly languages like X86 or MOS Technology 6502, this tutorial will help you get started with RISC-V assembly programming. By the end of this tutorial, you will have a solid understanding of RISC-V assembly and be ready to take on more advanced topics in Linux training.

Exploring RISC-V Simulator and Systems

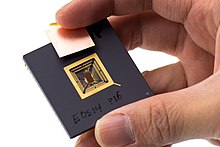

In the world of computer architecture, the RISC-V Instruction Set Architecture (ISA) has gained significant attention. To explore and understand this architecture, one can use a RISC-V simulator and system. These tools allow users to simulate the behavior of a RISC-V processor and gain hands-on experience with assembly language programming. By using a simulator, individuals can experiment with different instructions and understand how they affect the Central Processing Unit (CPU) and overall system performance.

This knowledge is essential for anyone looking to delve into the world of Linux training and gain a deeper understanding of computer hardware and software.

Advanced RISC-V Programming and Embedded Systems

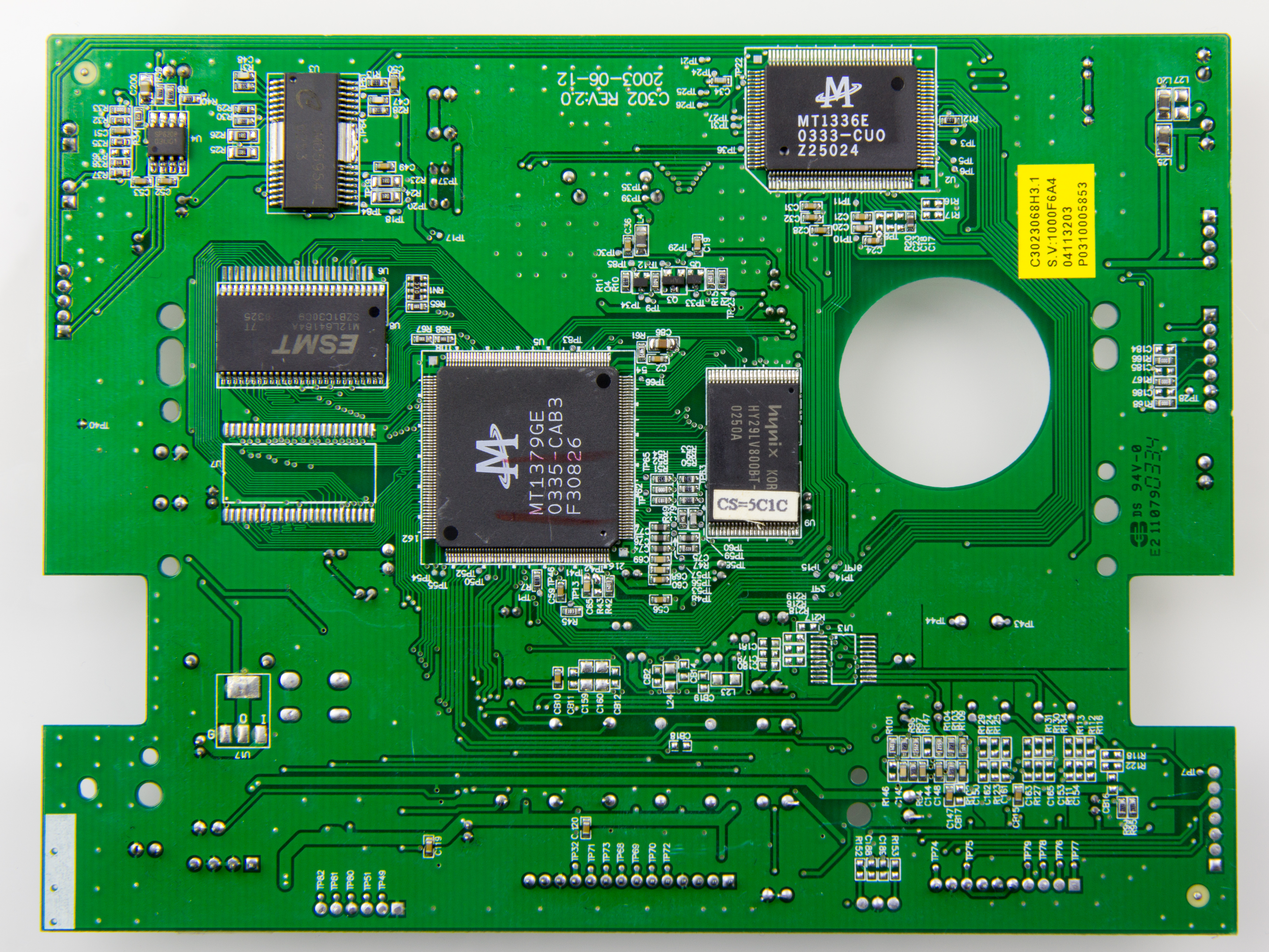

In this tutorial, we will dive into advanced RISC-V programming and embedded systems. With a focus on practical applications, we will explore topics such as the central processing unit and microprocessor architecture, including superscalar processors and out-of-order execution. We will also cover assembly language programming, specifically x86 assembly language, and its role in developing embedded systems. By the end of this tutorial, you will have a solid foundation in RISC-V programming and be well-equipped to pursue further Linux training.